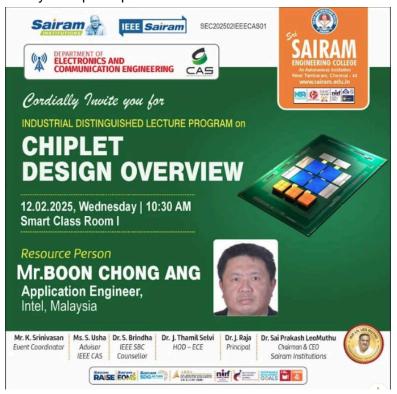

## Industrial Distinguished Lecturer Program by IEEE CAS Society (CASS) SBC60981AG

**Date: 12.02.25** Time: 10.30AM

**Venue: Smart Class Room I**

Industrial Distinguished Lecturer: Mr.Boon Chong Ang,

Application Engineer,

Intel, Malaysia.

Title: "Chiplet Design Overview: The Limit of Moore's Law and Challenges in Chiplets"

On 12th February 2025 at 10.30am, the Department of ECE, Sri Sairam Engineering College, in association with IEEE Circuits and Systems Society Student Branch Chapter organized the Industrial Distinguished Lecturer Program. It started with the Welcome Address and Introduction of the Resource Person by Prof. S, Usha, Advisor, IEEE Circuits and Systems Society, Sri Sairam Engineering College. Next, Mr.Boon Chong Ang took over the session. Nearly 100 participants attended this IDLP.

Professor explained that Chiplet design is an emerging solution to address the limitations of Moore's Law, which has seen slowing progress in transistor miniaturization. Moore's Law historically predicted that the number of transistors on a chip would double every two years, but physical and economic constraints are now limiting further gains. Chiplets allow for the modular integration of smaller, specialized components (chiplets) into a single package, enabling improved performance and scalability without the need for a monolithic design. This approach optimizes yield, reduces costs, and enhances flexibility. However, challenges in chiplet design include ensuring interoperability, managing complex packaging technologies, and dealing with the thermal and power constraints of integrating multiple chiplets. Additionally, designing a robust interconnect network between chiplets to ensure high-speed communication is a critical hurdle. Despite these challenges, chiplet-based architectures offer a promising path forward for continued innovation in semiconductor design. As the industry moves beyond Moore's Law, chiplets could play a key role in enabling the next generation of high-performance computing.

He also answered the queries asked by our students. The vote of thanks was proposed by Mr. K.Srinivasan, Professor from Sri Sai Ram Engineering College.

We take this opportunity to thank our **CEO sir, Principal sir, and HOD-ECE** for their support and guidance towards the successful completion of this Industrial Distinguished Lecturer Program.

Number of Participants: IEEE Members:70

Non-IEEE Member:30 CASS Members:40